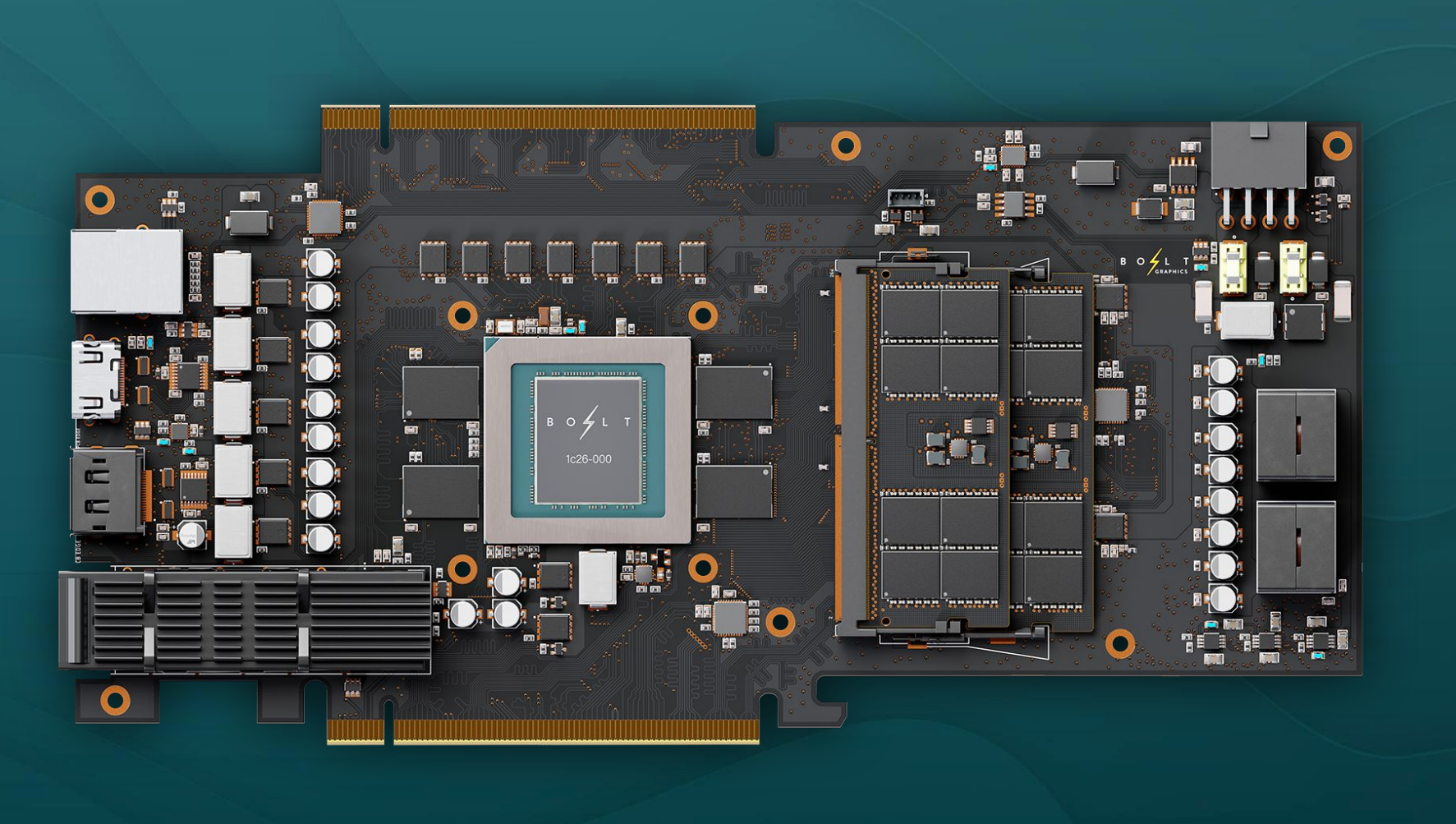

Intel has revealed new details about the die architecture of its upcoming Core Ultra 4 series, codenamed Nova Lake, confirming that the CPU cores will be fabricated on TSMC’s cutting-edge 2nm nanosheet process. This marks another step in Intel’s disaggregated tile-based design, where only the most performance-critical components—namely the CPU cores—receive the most advanced process node.

The Compute tile, housing the P-cores and E-cores, will come in two flavors for desktop processors. The mainstream variant will retain an 8P+16E configuration with a standard L3 cache, while the premium version introduces bLLC (big last-level cache), estimated to be 3–4 times larger than the regular L3. This design mirrors AMD’s 3D V-Cache approach, offering a significant performance boost for latency-sensitive workloads.

The premium Compute tile is projected to measure over 150 mm²—36% larger than the standard 110 mm² variant—solely due to the expanded cache. Beyond the Compute tile, Nova Lake integrates multiple components, including

- SoC Tile: Hosts low-power E-cores, DDR5 memory controllers, a 74 TOPS NPU, and the PCIe Gen 5 root complex.

- Graphics Tile: Likely built on Intel’s Intel 4 node (less advanced than the Compute tile but more advanced than the SoC tile).

This modular approach allows Intel to optimize each tile independently, balancing performance, power efficiency, and cost. The premium bLLC variant, in particular, positions Nova Lake as a direct competitor to AMD’s high-cache Zen 6 processors, such as the Ryzen 9 9950X3D2, which features a 192MB L3 cache.

Nova Lake is expected to launch in the second half of 2026, continuing Intel’s push toward a more flexible and performance-driven chiplet architecture.