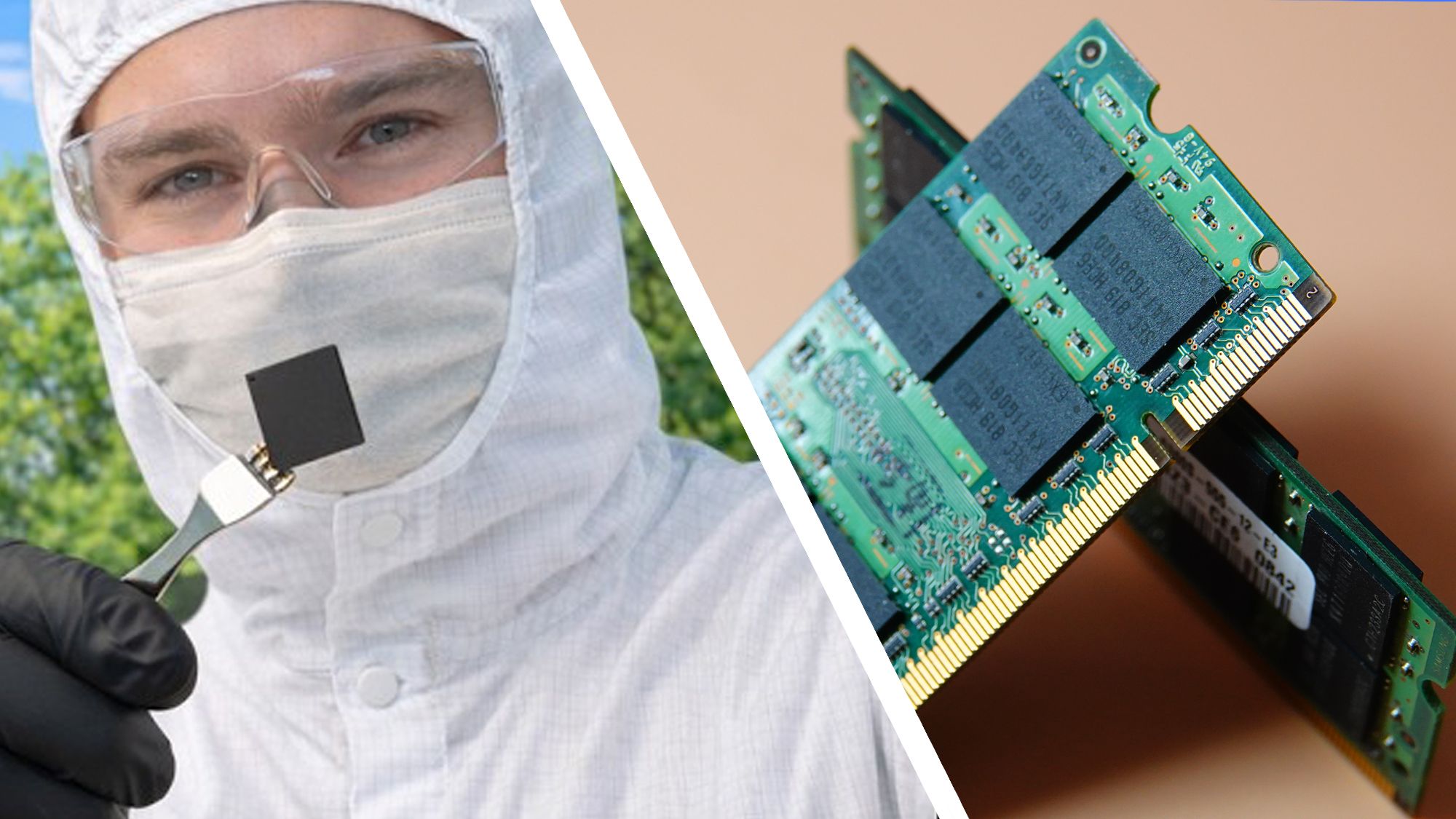

TSMC's decision to ramp up production for its 3nm and 2nm processes marks a significant shift in the semiconductor industry. While demand for high-performance chips remains robust, particularly in AI and mobile sectors, TSMC's move is designed to stabilize supply without compromising on technological advancements.

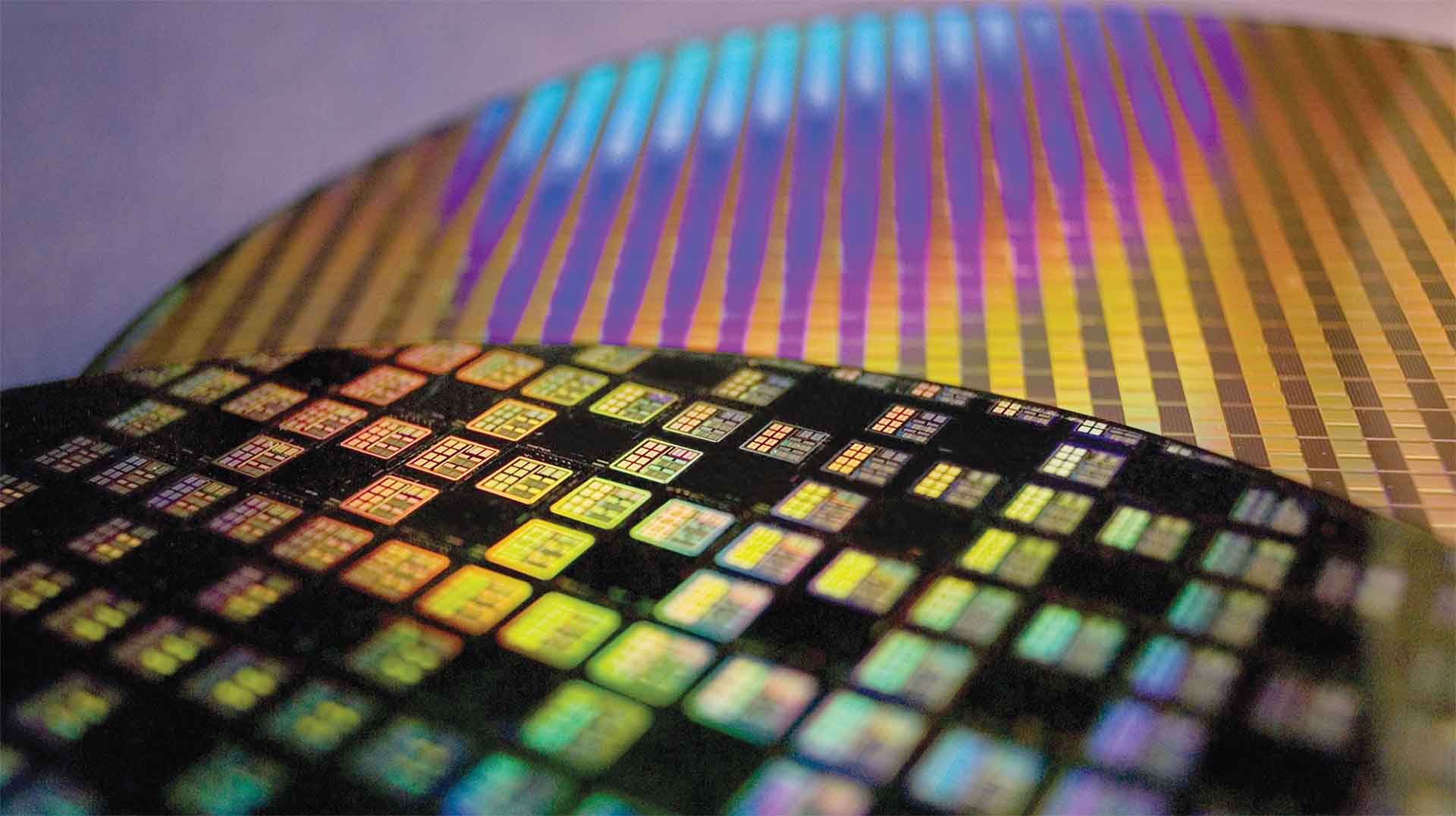

The company's focus on scaling these advanced nodes comes at a critical juncture. The 3nm process, expected to enter high-volume manufacturing in mid-2025, promises improvements in power efficiency—up to 10-15% over the 5nm node. This could drive broader adoption in energy-sensitive applications, including AI workloads and mobile devices. However, achieving the targeted 20% increase in wafer output by late 2026 will require overcoming operational hurdles, such as tooling readiness and yield optimization.

Industry Implications

The expansion reflects a broader industry trend toward balancing capacity with innovation. TSMC's historical caution about overpromising suggests that actual production levels may not meet projections, but the initiative itself signals a deliberate effort to meet growing demand while maintaining its edge in advanced node manufacturing.

For consumers and businesses, the potential benefits are substantial. More efficient chips could lead to longer battery life in smartphones, faster processing in data centers, and greater access to AI capabilities. However, these improvements will take time, with the first tangible impacts likely appearing in 2025 as 3nm-based products enter the market.

As TSMC scales its production lines, the semiconductor industry faces a pivotal moment. The ability to scale advanced processes without disrupting supply chains will determine how quickly innovation translates into real-world products. For now, the focus remains on steady progress—one wafer at a time.