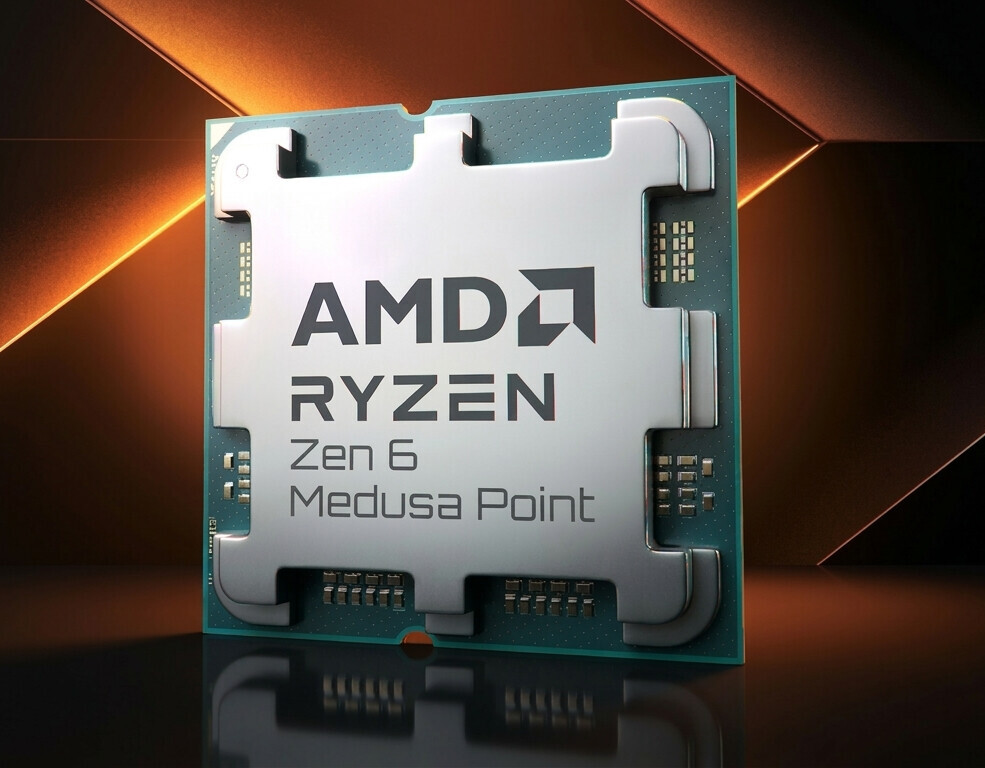

AMD’s next-generation 'Medusa Point' APU has emerged from early benchmarks with a performance profile that contradicts its lower operating frequency, positioning it as a serious contender against higher-clocked alternatives in both single-core and multi-core workloads.

The engineering sample, based on AMD’s 10-core, 20-thread 'Zen 6' architecture, achieved a Geekbench v6 single-core score of 2,300 and a multi-core score of 13,002 while running at just 2.4 GHz base clock—dipping to 2.0–2.1 GHz under load. When compared to the current 'Strix Point' APU, which operates at double the frequency but delivers slightly lower single-core performance and a modest multi-core advantage, the 'Medusa Point' sample stands out for its efficiency gains.

Key Specifications and Performance Insights

- Architecture: 10-core, 20-thread 'Zen 6'

- Process Node: TSMC 2 nm (compute dies), 3 nm (I/O die)

- Base Clock: 2.4 GHz (engineering sample)

- Load Clock: 2.0–2.1 GHz

- Performance Metrics: Single-core: 2,300 | Multi-core: 13,002 (Geekbench v6)

- Special Features: AVX-VNNI acceleration in FP16 precision

The discrepancy in performance suggests that the 'Zen 6' cores are not just faster but also more optimized for workload efficiency. Analysts speculate that this could stem from a combination of instruction set improvements and IPC (instructions per clock) gains, potentially in the high single-digit to low double-digit range over 'Zen 5'. The inclusion of AVX-VNNI support hints at enhanced AI and machine learning capabilities, though further benchmarks are needed to confirm real-world impact.

Why This Matters for Enterprise Buyers

The 'Medusa Point' APU’s efficiency could redefine power consumption and thermal constraints in enterprise systems, particularly for AI workloads where lower precision floating-point operations (FP16) play a growing role. If the trends hold, it may offer a compelling alternative to higher-clocked competitors, balancing performance with energy savings—critical factors for data center deployments.

That’s the upside—here’s the catch: The current benchmark represents an engineering sample, meaning production silicon could still undergo refinements. Additionally, while multi-core performance is impressive, single-core gains remain modest compared to the 'Strix Point' baseline. Enterprise buyers will need to weigh whether the efficiency improvements justify potential tradeoffs in sustained high-frequency performance.

What to Watch Next

The 'Medusa Point' APU is expected to debut at CES 2027, with official benchmarks and third-party validation likely following in mid-2027. Until then, the focus will remain on whether AMD can sustain these efficiency gains in mass production while addressing potential errata or thermal challenges. For now, the sample’s performance suggests a shift toward more optimized, lower-power designs—a trend that could reshape the APU landscape for both consumer and enterprise markets.