The AMD EXPO 1.2 specification marks a significant shift in how next-generation Ryzen processors will interact with DDR5 memory modules. For the first time, users won't need to rely on bypass mode—a workaround that has been a limitation for current platforms—to achieve optimal performance with CUDIMM DDR5 modules. This change aligns with AMD's vision of tighter memory-compute integration, which could lead to lower latency and more efficient power usage when paired with next-gen Ryzen CPUs.

Previously, EXPO-certified systems treated CUDIMM DDR5 as an external component, adding complexity and potential performance bottlenecks. EXPO 1.2 eliminates this by allowing the CPU to treat the memory as part of its unified architecture, similar to how it handles other types of memory. This shift is expected to benefit enthusiasts and power users who demand high performance in tasks like 3D rendering or AI workloads.

Key Improvements with EXPO 1.2

- Memory Integration: Full support for CUDIMM DDR5 modules (up to 64GB per module) on next-gen Ryzen CPUs, without the need for bypass mode.

- Performance Gains: Lower latency and improved bandwidth efficiency when memory is treated as part of the CPU's architecture, rather than an external component.

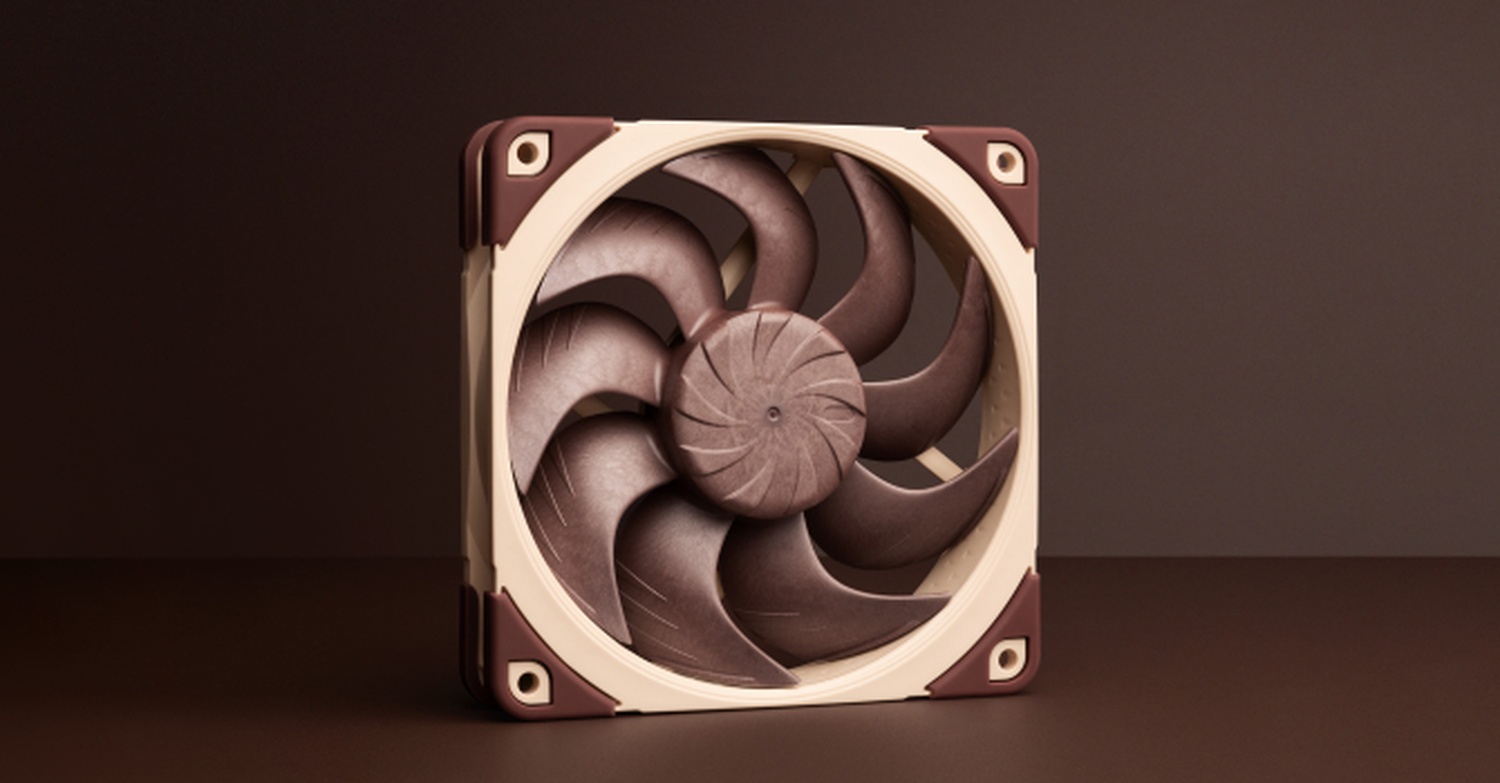

- Power Efficiency: Reduced power consumption due to tighter integration between the CPU and memory, leading to cooler and more efficient systems.

The specification also reflects a broader industry trend toward more cohesive memory-compute architectures. While the primary focus is on next-gen Ryzen CPUs, AMD hasn't ruled out potential backward compatibility for current platforms, though performance gains may be limited without deeper architectural changes.

Who Stands to Gain?

Enthusiasts and professionals working with memory-intensive tasks will likely see the most immediate benefits. For those involved in 3D rendering, AI workloads, or large-scale data processing, the ability to integrate DDR5 modules without bypass mode could translate to noticeable speed improvements. However, the full impact will be more apparent on next-gen Ryzen CPUs, where the architecture is designed to maximize this integration.

Current Ryzen systems will continue to operate in bypass mode for now, but AMD's move suggests that future updates or firmware changes could further optimize performance even on older platforms. The exact timeline for these improvements isn't clear, but the focus remains on next-gen CPUs where the architecture is primed for this level of integration.

Uncertainty and Future Outlook

The full implications of EXPO 1.2 are still unfolding, particularly regarding compatibility with existing memory modules and long-term support for current platforms. While AMD has outlined the direction, real-world testing will be necessary to confirm how much performance can actually be achieved through this tighter integration. For buyers, the key takeaway is that next-gen Ryzen systems will have a clear advantage in leveraging DDR5 memory, but whether current users see meaningful gains remains uncertain.

Current State and Future Expectations

The AMD EXPO 1.2 specification represents a step toward more efficient memory-compute architectures, but its full potential won't be realized until next-generation Ryzen CPUs are released. For now, users of current platforms should expect minimal changes unless AMD introduces firmware updates or other optimizations to bridge the gap. The focus for most buyers will remain on compatibility and performance when upgrading to new hardware, with the promise of smoother integration down the line.