Intel’s latest advancements in chip packaging are set to redefine how AI processors are built, with a focus on larger, more efficient designs that push the boundaries of what’s possible in semiconductor manufacturing. The company is expanding its package sizes to accommodate more high-bandwidth memory (HBM) stacks, but doing so comes with significant engineering challenges.

Key Upgrades in Intel’s Packaging Strategy

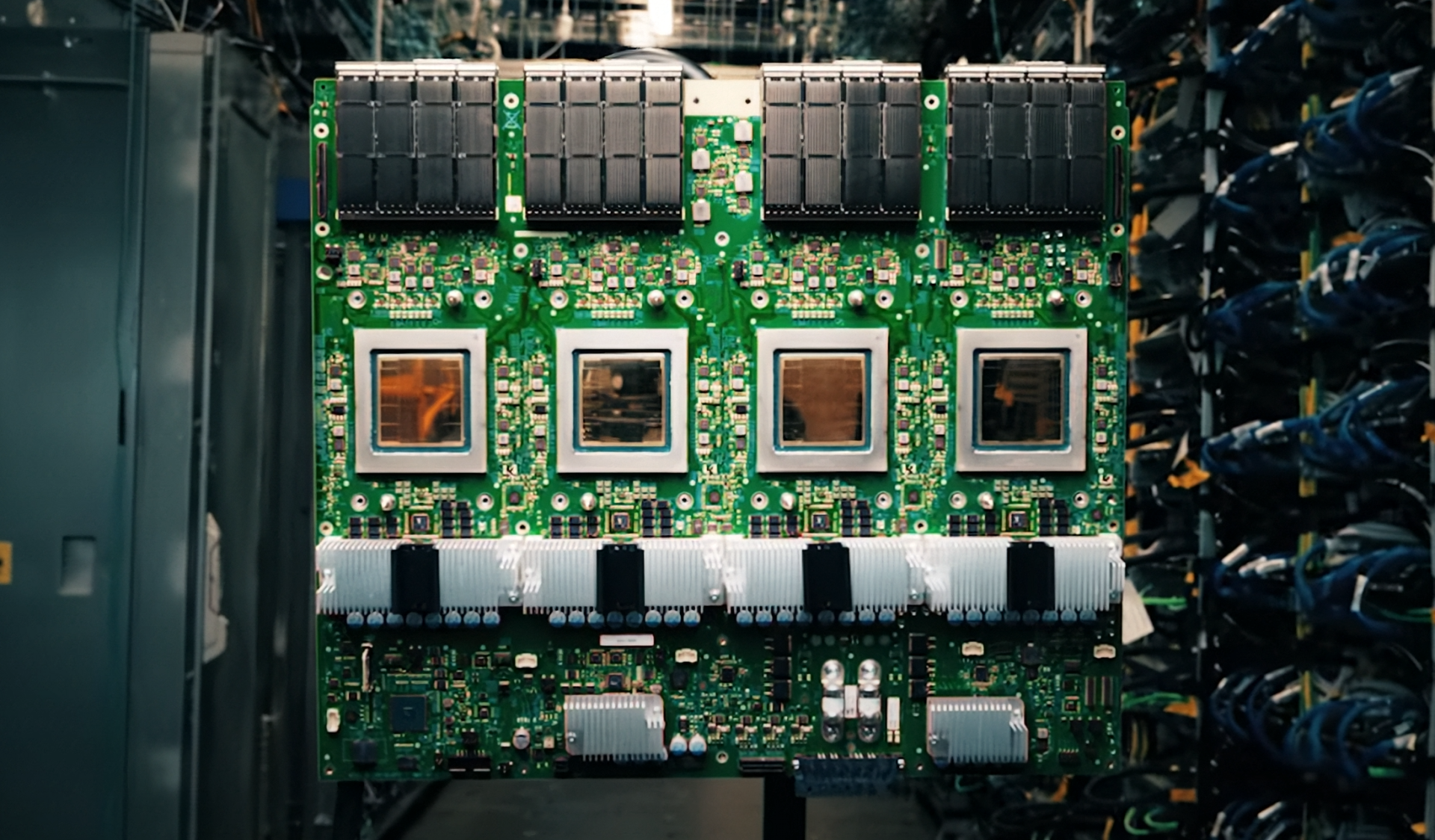

- Increased Package Size: Current 100 x 100 mm packages will grow to 120 x 120 mm, allowing for up to twelve HBM stacks—nearly double the current capacity.

- Future Scaling to 180 mm Width: By 2028, Intel aims for 120 x 180 mm packages capable of supporting twenty-four HBM stacks, addressing the insatiable bandwidth needs of AI chips.

- Enhanced Memory Integration: The latest EMIB-T technology integrates through-silicon vias (TSV) to support next-generation HBM4 memory, which is now in mass production. This tighter integration reduces latency and improves efficiency for AI workloads.

The shift to larger packages isn’t without its complications. Larger substrates are more prone to warpage during the manufacturing process, which can lead to yield losses and reliability issues. Intel will need to refine its processes to ensure these packages meet performance expectations while maintaining cost efficiency.

Why This Matters for AI and Beyond

- Bandwidth and Performance: Larger packages with more HBM stacks directly translate to higher bandwidth, a critical factor for AI training and inference. This could give Intel an edge in the competitive AI chip market.

- Cost vs. Efficiency Tradeoff: While larger packages offer performance benefits, the challenges of warpage and yield management must be overcome to avoid increasing costs. If successful, this approach could make advanced packaging more viable for a broader range of applications beyond AI.

The company’s investments in Malaysia—part of its foundry ambitions—highlight its commitment to scaling up production while addressing these manufacturing hurdles. The new facility, expected to launch later this year, will play a key role in testing and refining these larger package designs.

For AI chipmakers, the potential for more efficient designs with higher performance is compelling, but the success of Intel’s strategy hinges on whether it can balance size, efficiency, and manufacturing feasibility. If executed well, this could set a new standard for how chips are designed and manufactured, pushing the industry toward even more ambitious innovations.